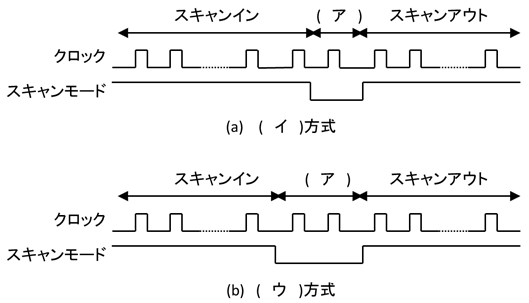

問題1:スキャン設計に基づく遅延テスト方法である、ブロードサイド方式(LoC方式とも呼ぶ)とスキュードロード方式(LoS方式とも呼ぶ)に関して、下記のタイムチャート中の名称について、正しい組み合わせを1~4の中から選びなさい。

-

- ア:シフト

- イ:ブロードサイド

- ウ:スキュードロード

-

- ア:シフト

- イ:スキュードロード

- ウ:ブロードサイド

-

- ア:キャプチャ

- イ:スキュードロード

- ウ:ブロードサイド

-

- ア:キャプチャ

- イ:ブロードサイド

- ウ:スキュードロード

《正答》

3.

- ア:キャプチャ

- イ:スキュードロード

- ウ:ブロードサイド

問題2:3次元デバイスにおけるTSV(Through Silicon Via)のテストに関して、以下の中で誤っているものを選びなさい。

- チップのTSVの数は多いが、テスト実行時間が小さい。

- 積層のためにダイが薄く研磨されており、ウェーハテストの際のプローブに大きな圧力がかけられない。

- 積層前のほうが積層後に比べてよりテストが困難である。

- TSVの間隔が狭く、狭ピッチのプローブカードが必要である。

《正答》

1.

チップのTSVの数は多いが、テスト実行時間が小さい。

問題3:複数のIP(Intellectual Property)コアを同時にテストすることによりテストコストの削減を図るコンカレントテストに関して、以下の中から正しいものを選びなさい。

- 生産数量の少ない大規模SoCにおいては、コンカレントテストによりテストコスト削減効果を得るのは不可能である。

- コンカレントテストで同時にテストする複数のIPコアは、すべて同一のIPコアである必要はない。

- IPコアのテストアクセスを統合すると、コンカレントテストの効率が低下する。

- コンカレントテストを用いても、高速I/Oのテストとロジックのテストを同時に行うことは不可能である。

《正答》

2.

コンカレントテストで同時にテストする複数のIPコアは、すべて同一のIPコアである必要はない。

問題4:フォトエッチング工程の処理の順番として、以下の中から正しいものを選びなさい。

-

- レジスト塗布 →

- 現像 →

- 露光 →

- エッチング →

- レジスト除去

-

- レジスト塗布 →

- 露光 →

- 現像 →

- レジスト除去 →

- エッチング

-

- レジスト塗布 →

- 現像 →

- 露光 →

- レジスト除去 →

- エッチング

-

- レジスト塗布 →

- 露光 →

- 現像 →

- エッチング →

- レジスト除去

《正答》

4.

- レジスト塗布 →

- 露光 →

- 現像 →

- エッチング →

- レジスト除去

問題5:LSIの積層技術について、インターポーザを用いて異なる種類のチップを積層して実装したものを何というか、以下の中から正しいものを選びなさい。

- チップサイズパッケージ

- 3Dデバイス

- ウェハレベルパッケージ

- 2.5Dデバイス

《正答》

4.

2.5Dデバイス

問題6:バイポーラトランジスタに関して、次の文章の空欄( )に入る正しい言葉の組み合わせを1~4の中から選びなさい。

バイポーラトランジスタは、ベース、エミッタ、およびコレクタの端子をもつ。npnトランジスタでは、( ア )はp型半導体で作り、( イ )はn型半導体で作る。トランジスタを動作させるためには、エミッタ―ベース間は( ウ )にし、ベース―コレクタ間は( エ )にする。

-

- ア:エミッタ

- イ:ベースおよびコレクタ

- ウ:逆バイアス

- エ:順バイアス

-

- ア:ベース

- イ:エミッタおよびコレクタ

- ウ:順バイアス

- エ:逆バイアス

-

- ア:コレクタ

- イ:エミッタおよびベース

- ウ:順バイアス

- エ:逆バイアス

-

- ア:ベース

- イ:エミッタおよびコレクタ

- ウ:逆バイアス

- エ:順バイアス

《正答》

2.

- ア:ベース

- イ:エミッタおよびコレクタ

- ウ:順バイアス

- エ:逆バイアス

問題7:半導体メモリのうち、データ保持のためのリフレッシュを必要とするものとして正しいものを、以下の中から選びなさい。

- SRAM

- FeRAM

- SDRAM

- MRAM

《正答》

3.

SDRAM

問題8:論理回路のレイアウトについて、 (ア~オ)を工程順に並べた正しい組み合わせを1~4の中から選びなさい。

( ア ) クロック配線

( イ ) フロアプラン

( ウ ) 論理ゲート間の配線(一般配線)

( エ ) 詳細配置

( オ ) 電源・グラウンドの配線

-

- イ →

- ア →

- ウ →

- オ →

- エ

-

- ア →

- オ →

- ウ →

- エ →

- イ

-

- イ →

- エ →

- オ →

- ア →

- ウ

-

- エ →

- イ →

- ア →

- オ →

- ウ

《正答》

3.

- イ →

- エ →

- オ →

- ア →

- ウ